사물인터넷(IoT)와 인공지능(AI)의 시대에 데이터 수집을 위한 센서 구성과 시스템 통합 또한 점점 복잡해지고 있다. AMD는 이러한 ‘인터페이스 집약적’ 엣지 애플리케이션에 최적화된 ‘스파르탄 울트라스케일+’ FPGA 제품을 선보이며, 빠르게 확장 중인 엣지 시장 공략을 제시했다.

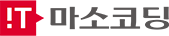

AMD는 5일(현지시각) 비용에 민감한 입출력 밀도 집약적인 애플리케이션에 최적화된 ‘스파르탄 울트라스케일+’ FPGA(Field-Programmable Gate Array, 프로그래밍 가능 집적회로 반도체) 제품을 공식 발표했다. 신제품은 작은 디바이스에서도 로직 셀 대비 많은 입출력(I/O)을 지원하며, 16나노미터(nm, 10억분의 1m) 공정과 메모리, PCIe 컨트롤러를 기본 내장해 기존 제품 대비 전력 효율도 크게 높아진 점이 눈에 띈다.

AMD의 ‘스파르탄(Spartan)’ FPGA 브랜드는 1998년 처음 선보인 이후 25년의 역사를 이어오며 의료나 항공우주, 과학계 등에 이르기까지 다양한 영역에서 사용되고 있다. 롭 바우어(Rob Bauer) AMD AECG 비용 최적화 반도체 마케팅 담당 수석 매니저는 “‘스파르탄’은 처음 등장할 때부터 다양한 미래지향적 기능을 작은 크기에 비용효율적으로 담아 다양한 시장 수요에 대응하는 것을 목표로 했다”고 소개했다.

AMD는 현재 시장에서는 ‘비용 효율적’ 솔루션에 대한 수요가 지속적으로 늘고 있다고 소개했다. 특히, 네트워크에 연결되는 IoT 디바이스의 급격한 성장세와 함께, 디바이스 수준에서 더욱 다양한 입출력 인터페이스에 대응하려는 수요도 늘어나는 상황이다. 이와 함께 디바이스 개발을 위한 개발자는 전 세계적으로 부족한 상황이며, 더욱 효율적인 디바이스 개발 환경이 요구되고 있다고 덧붙였다.

AMD의 새로운 ‘스파르탄 울트라스케일+(Spartan UltraScale+)’는 제품 구성 측면에서 뛰어난 로직 셀 대비 입출력 채널 수를 지원해, I/O 집약적 애플리케이션에서 더 많은 I/O를 작은 디바이스에서 사용할 수 있어 디바이스 크기와 비용을 절감할 수 있게 한다. 또한 16nm 공정을 사용해, 기존 28nm 기반 디바이스 대비 소비전력은 30%까지 줄였으며, DDR, PCIe 인터페이스의 ‘하드 IP’ 탑재로 전력 효율을 더 높였다고 소개했다.

보안 측면에서도, AMD는 ‘스파르탄 울트라스케일+’가 양자내성 암호화 기능을 포함해 AMD의 비용 최적화 솔루션 포트폴리오에서 가장 많은 보안 기능을 제공한다고 소개했다. 개발자 지원 측면에서는 이미 업계에서 검증되고 개발자에 익숙할 ‘비바도(Vivado)’ 디바인 스위트를 활용할 수 있으며, 이 디자인 스위트는 단일 툴에서 AMD의 전체 FPGA 포트폴리오와 디자인 과정 전반을 지원할 수 있다. 이와 함께, 공급 안정성 측면에서는 15년 이상의 제품 라이프사이클을 제공한다.

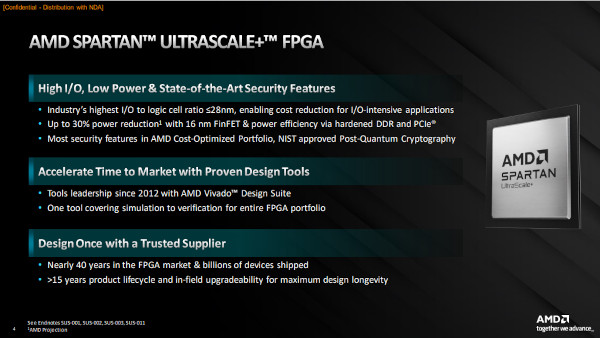

AMD는 ‘스파르탄 울트라스케일+’ FPGA가 특히 ‘엣지’에 최적화된 구성이라고 강조했다. 신제품은 이미 다른 제품군에서도 충분히 검증된 16nm 제조공정을 사용해 뛰어난 전력 효율을 제공하며, 블록 램과 울트라램(UltraRAM) 구성, 최대 384개의 DSP48E2 DSP(Digital Signal Processing) 블록도 제공해 엣지에서의 고성능 처리 환경도 제공할 수 있다.

미래지향적 역량 측면에서는 최대 572개의 I/O 지원이 중요한 장점으로 꼽혔다. ‘스파르탄 울트라스케일+’는 엣지 애플리케이션의 인터페이스 구현에 최적화돼, 로직 셀 규모 대비 I/O 수의 비율을 극대화한 점이 특징이다. 이를 통해 하나의 작은 FPGA에서도 많은 센서를 연결, 처리할 수 있다.

예를 들어, I/O 집약적 애플리케이션에서 200개 이상의 I/O가 필요할 때 지금까지는 좀 더 큰 디바이스인 ‘스파르탄 7S50’을 사용하면서 로직 셀 활용 효율이 떨어졌지만, 지금은 더 작고 저렴한 ‘SU10P’를 사용할 수 있다. 또한 3.2G MIPI 지원으로 고해상도 카메라까지 연결할 수 있어 활용 폭을 넓혔다.

LPDDR4x/5 메모리 컨트롤러와 PCIe 컨트롤러가 ‘하드 IP’ 형태로 기본 탑재돼 있는 점도 메모리 사용에 로직 셀 용량을 사용하지 않아도 돼 제품의 구성 유연성과 전력 효율, 비용 효율 등을 높인다. 예를 들면, 메모리 컨트롤러와 5만 개 로직 셀 확보가 필요할 때, 기존 ‘아틱스 7’에서는 메모리 컨트롤러 구현을 위한 3만 개의 로직 셀을 포함해 8만 로직 셀이 필요했지만, 스파르탄 울트라스케일+ 제품에서는 메모리 컨트롤러가 이미 있으므로 5만 로직 셀만 갖춘 더 작은 제품을 사용할 수 있다.

이 외에도, 개선된 공정과 ‘하드 IP’ 형태로 탑재된 메모리, PCIe 인터페이스를 통해 전력 소비 측면에서도 개선된 특징을 제공한다. AMD는 새로운 스파르탄 울트라스케일+ SU35P 제품이 기존의 28nm 기반 아틱스 7 7A35T 대비 소비전력을 30%까지 줄일 수 있다고 소개했다. 또한 인터페이스에서의 전력 효율 측면에서는, 스파르탄 울트라스케일+ SU200P는 기존 아틱스 7 7A200T 대비 메모리와 PCIe 대역폭당 전력소비량을 60%까지 줄였다고 밝혔다.

새로운 ‘스파르탄 울트라스케일+’ 제품군 또한 기존에 충분히 검증된 생산성과 신뢰성을 제공하는 AMD의 ‘비바도(Vivado)’ 디자인 툴에서 사용할 수 있다. 이 ‘비바도’는 이미 AMD의 FPGA를 사용하던 개발자들에 익숙한 툴이자, 업계에서 충분히 검증된 성능과 신뢰성을 제공한다는 점이 특징이다.

AMD는 이 툴의 장점으로, AMD의 모든 FPGA 포트폴리오를 단일 툴 환경에서 다룰 수 있다는 점과 FPGA 개발의 모든 단계를 단일 툴 환경에서 다룰 수 있다는 점을 강조했다. 또한 AMD는 ‘비용 효율적 제품군’에 이 툴을 프리 라이선스로 제공해 개발 환경에 대한 비용 부담을 줄여 경쟁력을 차별화했다고 덧붙였다.

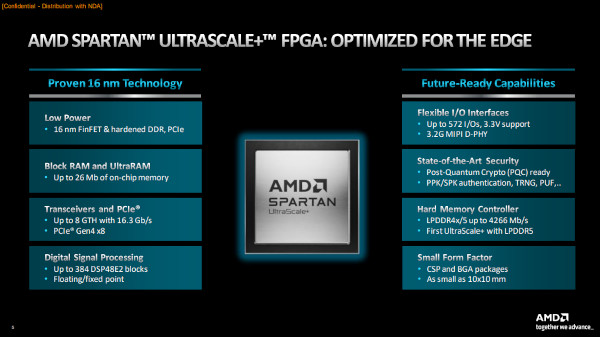

‘스파르탄 울트라스케일+’ 제품군은 1만1000개의 로직 셀을 갖춘 가장 작은 크기의 SU10P부터 21만8000개 로직 셀을 갖춘 가장 대형 디바이스인 SU200P까지 총 9개 제품군으로 구성됐다. 특히 ‘SU10P’는 1만1000개의 로직 셀 규모에도 최대 304개의 I/O를 갖춰, I/O대 로직 셀 비율 측면에서 특화된 모습이다. 또한 SU55P부터는 DDR 메모리 컨트롤러의 하드 IP가, SU65P부터는 메모리와 PCIe 컨트롤러의 하드 IP, GTH 트랜시버도 지원된다.

AMD는 이 ‘스파르탄 울트라스케일+’ 제품군에 대해 개발을 위한 얼리액세스 문서를 제공하고 있다. 개발 툴에서의 지원은 4분기 중, 실리콘 샘플과 평가 키트의 공급은 2025년 상반기 중 진행될 예정이다. 이 제품은 15년 이상의 제품 라이프사이클을 제공한다. AMD는 아직 공급되고 있는 구형 제품 대비로는 새로운 기능과 성능, 그리고 좀 더 장기적인 라이프사이클이 지원되는 점이 미래지향적인 측면에서 장점이 될 것으로 기대한다고 밝혔다.

권용만 기자 yongman.kwon@chosunbiz.com